HIGH PERFORMANCE COMPUTER ARCHITECTURE 23-11-2022

PLEASE REUTURN THIS SHEET ALONG WITH ALL THE SHEETS YOU WERE GIVEN

MATRICULATION NO.

SURNAME

FIRST NAME

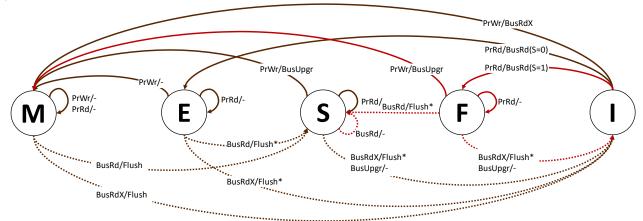

1) (POINTS 8/30) Consider a bus-based multicore that supports a new cache-coherence protocol called MESIF. Compared to the well-known MESI protocol, the MESIF protocol adds a 5<sup>th</sup> state called F (Forward). A copy in F state is like an S copy but the cache which holds it has the responsibility to provide (forward) the copy once a BusRd transaction involves that copy; at the same time, the S state is now simplified, as it doesn't have to respond to cache-to-cache transfers (Flush\* transactions) due to a BusRd. There will be at most one cache holding a copy in the F state; on a PrRd miss, if the are other shared copies, the state will be F, whilst if another F copy observes the BusRd will go to S. Both F and S states are clean shared states. If the copy in F state is eventually evicted, there will be no copy in the F state: in this case the copy will be provided by the memory. 1a [Points 8/30] Draw the diagram of the MESIF protocol according to the above description.

1b) [Points 22/30] Assuming a cost of 1cc (1 clock-cycle) for read/write operations, 90cc for BusRd or BusRdx transactions, 60cc for BusUpgr, 20 cc for Flush\* and 30cc for Flush. Evaluate the total cost (in clock-cycles) for the following streams:

|   | Core Operation | C1 | C2 | C3 | Bus Transaction | Data from | Cycles |  |  |  |

|---|----------------|----|----|----|-----------------|-----------|--------|--|--|--|

|   | PrRd1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd1          |    |    |    |                 |           |        |  |  |  |

|   | PrWr1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd2          |    |    |    |                 |           |        |  |  |  |

|   | PrWr2          |    |    |    |                 |           |        |  |  |  |

|   | PrRd2          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr2          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd3          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr3          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd3          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr3          |    |    |    |                 |           |        |  |  |  |

|   | TOTAL          |    |    |    |                 |           |        |  |  |  |

|   | Core Operation | C1 | C2 | C3 | Bus Transaction | Data from | Cycles |  |  |  |

| Ī | PrRd1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd2          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd3          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr2          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr3          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd2          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd3          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr3          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr1          |    |    |    |                 |           |        |  |  |  |

|   | TOTAL          |    |    |    |                 |           |        |  |  |  |

|   | Core Operation | C1 | C2 | C3 | Bus Transaction | Data from | Cycles |  |  |  |

|   | PrRd1          |    |    |    |                 |           |        |  |  |  |

| I | PrRd2          |    |    |    |                 |           |        |  |  |  |

| Ī | PrRd3          |    |    |    |                 |           |        |  |  |  |

| Ţ | PrRd3          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr1          |    |    |    |                 |           |        |  |  |  |

| Ī | PrWr2          |    |    |    |                 |           |        |  |  |  |

| Ē | PrWr3          |    |    |    |                 |           |        |  |  |  |

## EXERCIZE 1a)

First, we start drawing the states of the MESI protocol (except for S state – see brown lines), then let's focus on S and F states. **S-state**: PrRd and PrWr are exactly as in MESI; also, BusRdX and BusUpgr, as in MESI, cause an invalidation of the local copy; BusRdX will also provide a copy (useful, e.g., in the case of write-miss (PrWr from I)) to be written partially;

differently from MESI, now a BusRd - snooped from a cache with a copy in S-state – will NOT be followed by a Flush\*: the cache with the shared copy in F-state will provide such copy, eventually – if such copy has been evicted in the meantime, the memory will intervene.

**F: state**: PrRd and PrWr are exactly like for the S-state (remember that F is a shared clean state); like in S-state, the BusRdX and BusUpgr transaction cause a local invalidation, with the Flush\* following the BusRdX; we enter the F-state on a read-miss once the shared-line indicates that there exist other copies in the system (S=1), so the newly acquired copy is shared; when a BusRd is snooped, this cache has the responsibility to provide the copy via a Flush\* and its state will be then demoted to S (its duty is finished, the other cache with the shared copy will get the new copy in F state – it is the only possibility for a BusRd – the other is with S=0, which is not this case).

## **EXERCIZE 1b)**

|          |                | <b>C1</b> | ~~     | ~ ~ ~  | Dese march set i su          | Data Gara | <b>A</b>       |

|----------|----------------|-----------|--------|--------|------------------------------|-----------|----------------|

|          | Core Operation | C1        | C2     | C3     | Bus Transaction              | Data from | Cycles         |

| Ēų       | PrRd1          | E         | I      | I      | BusRd(S=0)                   | Mem       | 90             |

| H        | PrWr1          | м         |        |        | -                            | -         | 1              |

| ທ        | PrRd1          | M         |        |        | -                            | -         | 1              |

| E<br>N   | PrWr1          | М         |        |        | -                            | -         | 1              |

| 2        | PrRd2          | S         | F      |        | BusRd(S=1),Flush             | C1        | 90+30          |

| н        | PrWr2          | I         | М      |        | BusUpgr                      | -         | 60             |

| 1        | PrRd2          |           | М      |        | -                            | -         | 1              |

| tream    | PrWr2          |           | М      |        | -                            | -         | 1              |

| Ω<br>Δ   | PrRd3          |           | S      | F      | BusRd(S=1),Flush             | C2        | 90+30          |

| ч        | PrWr3          |           |        | М      | BusUpgr                      | -         | 60             |

| ι<br>Γ   | PrRd3          |           |        | М      | _                            | -         | 1              |

| Ŋ        | PrWr3          |           |        | м      | -                            | -         | 1              |

|          |                |           |        |        |                              | TOTAL     | 457            |

|          | Core Operation | C1        | C2     | C3     | Bus Transaction              | Data from | Cycles         |

| ц        | PrRd1          | Е         | I      | I      | BusRd(S=0)                   | Mem       |                |

| -i       | PrRd2          | S         | F      |        | BusRd(S=1),Flush*            | C1        | 90+20          |

| Ŋ        | PrRd3          | S         | s      | F      | BusRd(S=1),Flush*            | C2        | 90+20          |

| Ĩ        | PrWr1          | м         | I      | I      | BusUpgr                      | -         | 60             |

| 4        | PrWr2          | I         | м      |        | BusRdX, Flush                | C1        | 90+30          |

| N        | PrWr3          |           | I      | м      | BusRdX, Flush                | C2        | 90+30          |

| <u>_</u> | PrRd1          | F         |        | s      | BusRd(S=1),Flush             | C3        | 90+30          |

| stream   | PrRd2          | S         | F      | S      | BusRd(S=1),Flush*            | C1        | 90+20          |

| a)       | PrRd3          | S         | S      | S      | -                            | _         | 1              |

| й        | PrWr3          | Ĩ         | I      | M      | BusUpgr                      | -         | 60             |

| ų        | PrWr1          | м         | -      | I      | BusRdX,Flush                 | C3        | 90+30          |

| Ŋ        |                |           |        | -      | 2001001/11001                | TOTAL     | 1021           |

|          | Core Operation | C1        | C2     | C3     | Bus Transaction              | Data from | Cycles         |

| ÷ų –     | PrRd1          | E         | I      | I      | BusRd (S=0)                  | Mem       | 90             |

| Ч<br>М   | PrRd1<br>PrRd2 | S         | F      |        | BusRd(S=1),Flush*            | C1        | 90+20          |

| 1        | PrRd2<br>PrRd3 | S         | r<br>S | F      | BusRd(S=1),Flush*            | C1<br>C2  | 90+20          |

| E<br>E   | PrRd3          | S         | s      | F      | -                            | -         | <u> </u>       |

|          | PrWr1          | M         | I      | r<br>I | BusUpgr                      | -         | 60             |

| າ<br>I   | PrWr1          | M         | -      |        | Busopyr                      | -         | 1              |

| Ė        | PrWr1<br>PrWr1 | M         |        |        | -                            | -         | 1              |

| eam      |                |           |        |        |                              | -         | 1              |

| Ð        | PrWr1          | M         |        |        | -                            |           |                |

| й<br>Ч   | PrWr2          | I         | M      | м      | BusRdX,Flush<br>BusRdX,Flush | C1<br>C2  | 90+30<br>90+30 |

| 1        | PrWr3          |           |        |        |                              |           |                |